# 12T MEMORY CELL FOR AEROSPACE APPLICATIONS IN NANOSCALE CMOS TECHNOLOGY

<sup>1</sup>Aade Kailas Ukala,<sup>2</sup>Lingampally Shivprasad,<sup>3</sup>S.Ravinder,<sup>4</sup>T.Sukhdev <sup>1234</sup>Assistant Professor Department Of ECE Kshatriya College of Engineering

#### Abstract—

The size of semiconductors and the distances between them are rapidly shrinking as technology advances. As a result, SRAM cells used in aerospace applications become more susceptible to soft-error when the fundamental charge of the fragile nodes decreases. Single-event upsets (SEUs)may cause data inversion if a radiation particle hits a sensitive node in a typical 6T SRAM cell.To lessen the impact of SEUs, this paper proposes a Soft-Error-Aware Read-Stability-EnhancedLow-Power12T (SARP12T) SRAM cell. SARP12T's performance is evaluated in relation to those of other recently released soft-error-aware SRAM cells such as QUCCE12T, QUATRO12T, RHPD12T, and RSP14T. Even if the values of the sensitive nodes in SARP12T areflipped due to a radiation attack, the data may be recoverable. SARP12T is resilient to storagenode-pair-initiated single-event multi-node upsets (SEMNUs). The '0' storing memory nodes in the proposed cell are easily accessible through the bit line during read operation and are highly resistant to interruptions. SARP12T is also the most efficient method of holding in terms of energy consumption. SARP12T out performs competing cells in terms of write performance, and its write latency is much lower. The suggested cell achieves all of these advantages with just a little increase in read latency and read/write energy.

Keywords—Aerospace, SARP12T,QUCCE12T, SRAM DOI Number: 10.48047/NQ.2022.20.12.NQ77759

#### I. Introduction

Thestrongionizingeffectofradiationnearnuclearreactor sandin space has the potential to impair ordestroy electrical infrastructure. Ionizing radiation has been linked to circuit failures, notablyin data storage devices. The scientific community uses the term "single event upset" (SEU) todescribetheoccurrenceofseveralionizingeffectsofra diationatonce[1,2].Ontheonehand,theidea that this radiation doesn't have any effect on long-term memory seems conceivable. Whenmany events occur at once, it may cause an electronic equipment to malfunction, а

phenomenonknownasthe"singleeventmulti-

upseteffect"(SEMU)[22].Resetting[7]theelectricalcycle withsoftware that employs state machines to recognize prior states might reduce radiation risks.Spending a little amount on space-related

## NeuroQuantology2022;20(12): 4337-4341

applications won't alter this fact [4]. Bit flipping inionizing CMOS [16] memory is the source of a soft mistake [17]. This impact is due to the expansion of pores in the oxide layer. This strategy makes data storage very sluggish to access. When evaluating SRAM memory in the presence of ionizing radiation, it may be helpful to use awrite cycle of different time and complexity to better display the findings. Every new generation of technology results in smaller and more powerful integrated circuit machines. The goal of thistechnique, which makes use of integrated circuits, is to increase output by packing as manycomponentsintoagivenspaceas feasible. AsMoore'slawhasbeenroughlyfollowed,thesizeoftransi stors, the fundamental building blocks of memory cells, ha srisen.So, itstandstore as on that cell density will gradually reduce with each succeeding generation [1]. Due to the small size of the transistors used in each individual cell contemporary technology,

constitutes a nanoscalesystem; this is how SRAMmetal-oxide-semiconductor compatible (CMOS) memory is created.As a result, SRAM chips are able to function at steadily decreasing voltages. The InternationalTechnologicalStrategyforSemiconductors (ITRS)predictedthatthistrendwouldreverse, but the opp osite has already occurred. The scaling limitation on the threshold the voltage of transistorkepttheleakagecurrenttoanacceptablelevel[ 2].Thesestaticrandomaccessmemories(SRAMs)areess entialtotheoperationofmanycontemporaryelectronicd evices. This need has been met in large part through the all ocationofdedicatedspace.Costsareanticipatedtoincrea seasthepredicted number of patients exceeds 90% [3. The technicians are trying to fit as many SRAMcellsastheycanintoeachpart.Becauseitresultsinc ellsthataresmaller insize,thisprocedureiscrucial for improving the technology. SRAMs have transistors that are normally as small and ashigh up in the architecture as is practicable. Additionally, the voltage is maintained low to easestrainontheelectricalsystem.However,thereduce dpowerusagewasonlypartiallyimplementedin

practice. With the development of new technologies, SRAM devices have become smaller and use less power; nonetheless, the design still has to overcome significant two obstacles, namely, cells tability and transient event radiation. This st udyfocusesonthelatterphenomenon.However,therear ealsoinquiriesintoSRAMdependabilityconcerns.Interm sofregionalradiation,SRAMsare crucial. They might be badly damaged by single-event upsets (SEUs), which are triggered by a single particle of energy. These failures are categorized as soft errors (SE) since they do notpermanently harm the circuit. When massive particles collide, thev release electron-hole pairs(SEUs), which are gathered in a sensitive region and u tilizedtocontrolthecircuit'spowersupply. A node in an SRAM array may check the status of a cell and change the data stored in it if thereisenoughnoise. There is not ruth to the seclaims at all .OneormoreSRAMcellsmighthavetheirdata corrupted by a passing particle.

I. PROPOSEDMETHOD

This novel radiation-hardened-by-design (RHBD)12T storage facility features aneasily implementable layout-topology and also takes into consideration the physicalmechanism of upset in soft faults. The validation results show that the proposed 12Tcell can provide significant radiation resistance. The predicted 12T cell requires

moreroom, energy, and time to read and write than a13T cell. The 986.2 mV marginof staticnoise in the hold is more than what a 13T cell can achieve. The errorcorrecting capabilities of the recommended 12T ce llmake it more trust worthy. These days, CMOS tech nology is ubiquitous in the electronics sector. The aircraft industry is another that benefits greatly from

CMOStechnology.Memoriesaretheprimary datastoragemechanisminmanyaeronauticalapp lications.CMOStechnologyisusedintheproductio n of SRAM cells, a kind of memory. The main problem with long-termmemory is singleeventdisruptions (SEUs), which are brought on by particles of radiation. Rising urbanization is directly responsible for the SEUs. As CMOS processtechnology has advanced, both the critical charge and supply voltage have decreased.A approach free of these SEUs is needed for use in aircraft systems. Where exactly dothey exist in the very radioactive void between the stars? Methods that are radiation-hardenedby design (RHBD)thatare resistanttosofterrorsarecurrentlybeingresearch ed. The primary contribution of this study is a propo salforalow-profile, high-

- reliabilityRHBDmemorycell.

- "Adiabaticlogic"referstolow-

powerelectricalcircuitsthatmaybeemployedinei therdirection. During the adiabatic phase, there is no change in the total quantity of heat orenergy in thesystem,thusthename.Energy dissipationisgreatlyimprovedbydecreasingcircui tsizeandincreasingcircuitfineness,whichhasbee namajormotivationforstudyingadiabaticcircuits

# A. SCRLNAND

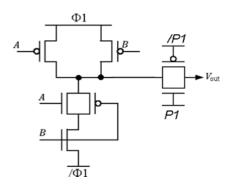

Understanding the bigpicture behind this group of genes may require dissecting the SCRL NA ND completeloopshowninFigure1.

ThisNDusestrapezoidalclocks(Kin1 and/Kin1)to powerthetopandbottomtracks,rather than the more conventional Vdd and Gne 1. There has been no change to thissection. With the exception of P 1, which is connected to Gnd, and /P 1, which is connected to Vdd, all components are linked to Vdd/2 in the first position, renderingthe switch gate superfluous. The transmission gate is turned on once P 1 and P 1 areconfigured.Firststeps.VddandGndarethencre atedfromthe/first1and/first1Vdd/2nodes. At 4338

NEUROQUANTOLOGY | October 2022 | VOLUME 20 | ISSUE 12 | PAGE 4337-4341 | DOI: 10.48047/NQ.2022.20.12.NQ77759 Aade Kailas Ukala et al/ 12T MEMORY CELL FOR AEROSPACE APPLICATIONS IN NANOSCALE CMOS TECHNOLOGY

this stage, the NA ND of both a and b go through the same nonadiabaticdoorcalculation.Oncetheoutputisbein gutilizedbythesubsequentgate,thetransmitting gate may be gradually disabled. The input may be adjusted and the nextphase initiated once the sum of phases 0 and 1 reaches Vdd/2 again. Since a deviationfrom Vdd/2 would violate the first criterion, a resistor must be disabled and the railsresettothisvalue. P-

MOS'sfunctionwhencoupledwithBinputisuncle ar.Pleasereviewthecircumstancesbehind thedisappearance of the transistor.Timesoftheeleventhday.

#### Figure1 :SCRLNAND

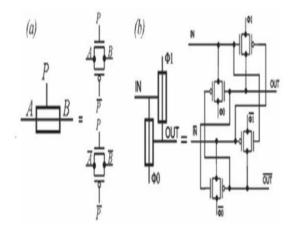

#### B. 2LAL

Frank's[2] Another significant class of adiabatic circuits is the 2LAL family. Thisseries, like SCRL, has complete plumbing all the way to the gate. Figure 2(a) depicts the fundamental components of 2LAL, a pair of transmission gates used to represent the signals A and A. Because of its simpl icity and independence from CMOS, 2LAL is wells uited for implementation in cutting edge devices.

Two transmission gates make up the 2LAL basic buffer feature, seen in Figure 2(b).Eachtrapezoidalclock'szero

pointonthefourthcyclehappensoneandaquart ertimeslater than the other. Both vertices start out with a value of 0 at the beginning. If theinputis1,the state willchangefrom0 to1overtime.Whenwegoonto"phase 1,"

Figure 2: 2LALBasicGate(a) andBuffer(b) Whentheinput is1,theoutputand inputarebothsetto

1, and the transistor is disabled to save power. Finally, switch the input back to 0 and keep cycling between 1 and 0. The pipeline is ready to accept an ewinput after the output passes through the next gate and reverts to 0. 2LAL can build inverters quickly since rails may cross from one portto another.

- II. RESULT

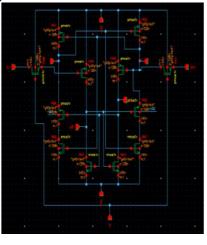

- A. Proposed schematic

Figure 3: Proposed schematic

4339

#### Figure4 : proposed schematic simulation result

#### A. DELAY

| Parsing            | 0.01 | seconds |

|--------------------|------|---------|

| Setup              | 0.05 | seconds |

| DC operating point | 0.07 | seconds |

| Transient Analysis | 0.03 | seconds |

| Overhead           | 0.91 | seconds |

|                    |      |         |

| Total              | 1.07 | seconds |

#### A. POWER

Power Results

VVoltageSource\_3 from time 0 to 100 Average power consumed -> 5.594084e-011 watts Max power 2.061770e+000 at time 8.025e-008 Min power 8.198842e-003 at time 3.20774e-008

#### CONCLUSION

Theunique12TRHBDmemorycelldevelopedher elessenstheeffectofsoftmistakesin standard 65 nm CMOS technology. The proposed memory cell is an advancementover prior designs in a number of respects; most importantly, it is more resistant todisturbances that damage several nodes. 1000 MC simulations further corroborate theprocess's SEU robustness bv demonstrating that no changes to the process affect theSEU's stability. Some high-speed applications may be slowed down by the proposed12T memory cell because of its slower read access time compared to existing memorytechnologies.Memorysize,robustness, andreliabilitymaybeoffargreaterimportancein mission-critical aircraft applications. In light of this, the RHBD 12T memory cellreported in this paper is, from the standpoint of a critical application designer, anexcellentdesignforradiationresistancewhen comparedtootherstate-of-the-arthardened memory cells. Increasing the paper's speed while decreasing its footprint is acommonmethodofimprovement. OneofthetrickiestNano-

scaledependabilityissuestosolveistheBTI,which modifiesthe transistor's Vth value. Changing the Vth of SRAM transistors degrades the qualityofSNMs.Inthisstudy,wedescribeasensor thatcandetectBTIdeteriorationinSRAMcells with high accuracy, allowing for the monitoring of this process over time. Thepeak Ivdd/Ignd of the SRAM block during a write

operation may be used as a eISSN1303-5150

proxyfortheNBTI/PBTIagingofindividualSRAMce IIs.TheCCVSmeasuresandconvertsthis current to voltage. The fundamental frequency of the VCO's oscillation is set bythemaximumvalueofthisvoltage.Thefrequen cyoftheoscillationsmaybecompared to that of newly created cells to observe the impact of BTI. Reading the appropriateiteminthe SRAMmayrevealthe roworcell's BTIcondition.

### REFERENCES

[1] E. Ibe, H. Taniguchi, Y. Yahagi, K.-I. Shimbo, and T. Toba, "Impact of scaling onneutroninduced soft error in SRAMs from a 250 nm to a 22 nm design rule," IEEETrans.ElectronDevices,vol.57,no.7,pp.1527 -1538,Jul.2010.

[2] P.E.DoddandL.W.Massengill, "Basicmechani smsandmodelingofsingle-eventupset in digital microelectronics," IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 583–602, Jun. 2003.

[3] R. C. Baumann, "Soft errors in advanced semiconductor devices part I: The threeradiationsources,"IEEETrans.DeviceMater. Rel.,vol. 1,no.1,pp.17–22,Mar.2001.

[4] H. L. Hughes and J. M. Benedetto, "Radiation effects and hardening of MOStechnology:Devicesandcircuits,"IEEETrans. Nucl.Sci.,vol.50,no.3,pp.500–521,Jun.2003.

[5] C. Boatella, G. Hubert, R. Ecoffet, and S. Duzellier, "ICARE on-board SAC-C:Morethan8yearsofSEUandMCU,analysisandp rediction,"IEEETrans.Nucl.Sci.,vol.57,no.4,pp.2 000–2009,Aug.2003.

[6] Y.Bentoutou, "ArealtimeEDACsystemforap plicationsonboardearthobservation small satellites," IEEE Trans. Aerosp. Electron. Syst., vol. 48, no. 1, pp.648–657, Jan. 2012.

[7] P. D. Bradley and E. Normand, "Single event upsets in implantable cardioverterdefibrillators,"IEEETrans.Nucl.Sci., vol.45,no.6,pp.2929–2940,Dec.1998.

[8] M. L. McLain, H. J. Barnaby, I. S. Esqueda, J. Oder, and B. Vermeire, "Reliabilityof high performance standard two-edge and radiation

NEUROQUANTOLOGY | October 2022 | VOLUME 20 | ISSUE 12 | PAGE 4337-4341 | DOI: 10.48047/NQ.2022.20.12.NQ77759 Aade Kailas Ukala et al/ 12T MEMORY CELL FOR AEROSPACE APPLICATIONS IN NANOSCALE CMOS TECHNOLOGY

hardened by design enclosedgeometrytransistors,"inProc.IEEEInt. Rel.Phys.Symp.,Apr.2009,pp.174–179.